RAM revealed

Memory Research

Random Access Memory (RAM) has always been used by processors and computer systems to store the programs currently being executed along with their data. Back in the 1980s, operating systems started to use excess RAM as a page cache for caching disk access [1].

The technology used since the start of the millennium, however, is Double Data Rate Synchronous Dynamic Random Access Memory (DDR-SDRAM) [2]. In contrast to its predecessor, SDRAM, DDR-SDRAM transfers data on both the rising and falling edges of the clock signal, thus doubling the data rate.

DDR-SDRAM has reached the third generation now, and work is in progress on the fourth (Table 1). Current systems use DDR3; but, because servers and desktops are typically deployed for three to five years, many datacenters and offices still use DDR2 RAM. Initial prototypes of DDR4 also exist. However, because the energy efficiency of DDR3 continually improves and Load-Reduced (LR)-DIMMs will support even larger DDR3 memory configurations in future, analysts don't anticipate a significant breakthrough for DDR4 until 2014.

Tabelle 1: DDR Generations

|

Property |

DDR1 |

DDR2 |

DDR3 |

DDR4 (in development) |

|---|---|---|---|---|

|

Number of contacts |

184 |

240 |

240 |

Still unknown |

|

Operating voltage (V) |

2.5 |

1.8 |

1.5 (DDR3L: 1.35; DDR3U: 1.25) |

1.2 |

|

Chip (I/O clock frequency, MHz) |

DDR-200 (100)DDR-266 (133)DDR-333 (166)DDR-400 (200) |

DDR2-400 (200) DDR2-533 (266) DDR2-667 (333) DDR2-800 (400) DDR2-1066 (533) |

DDR3-800 (400) DDR3-1066 (533) DDR3-1333 (666) DDR3-1600 (800) DDR3-1866 (933) DDR3-2133 (1066) |

DDR4-1600 (800) to DDR4-3200 (1,600) |

|

Prefetching |

Dual prefetch (2-bit) |

Quadruple prefetch (4-bit) |

8x prefetch (8-bit) |

8x prefetch with two or four bank groups |

|

Typical structure widths (nm) |

150, 100 |

100, 90, 80, 60 |

80, 60, 50, 40, 30, 25 |

30 |

Error Correction

No matter which generation of DDR you look at, you always have a choice between legacy memory modules and memory modules with error correcting. The latter include an Error-Correcting Code (ECC) mechanism and are mainly found in server applications. The benefits are obvious: Because of the integrated Hamming code, ECC memory modules can identify and correct 1-bit errors, and 2-bit errors are at least identified.

The mainboard and processor need to support error correction for ECC; if they do not, ECC modules will run without providing ECC support. Error-correcting modules are visibly identifiable if you check the number of soldered memory chips. Although legacy Dual Inline Memory Modules (DIMMs) typically have eight memory chips on one side, ECC DIMMs house a ninth memory chip. ECC modules are slightly more expensive than the legacy modules, but the enhanced capability is definitely worth the price in server operations.

Buffer Chips

Desktop computers and servers with one CPU socket use what are known as unbuffered DIMMs, which means the memory controller accesses the memory chips directly. This setup allows for a good price/performance ratio, but because the signals travel directly from the memory controller to each memory chip, the maximum amount of memory is restricted. This explains why dual-CPU systems use different memory modules that contain buffer chips or registers, thus extending the limits. If you look at the dual-CPU systems in the Intel core microarchitecture (Xeon 5100, 5200, 5300, and 5400), you will see that they all used fully buffered DIMMs (FB-DIMMs) on the basis of DDR2.

On the downside, the Advanced Memory Buffer (AMB) that an FB-DIMM also features will increase energy requirements and produce more heat – this explains why the manufacturers fitted cooling fins to the memory modules.

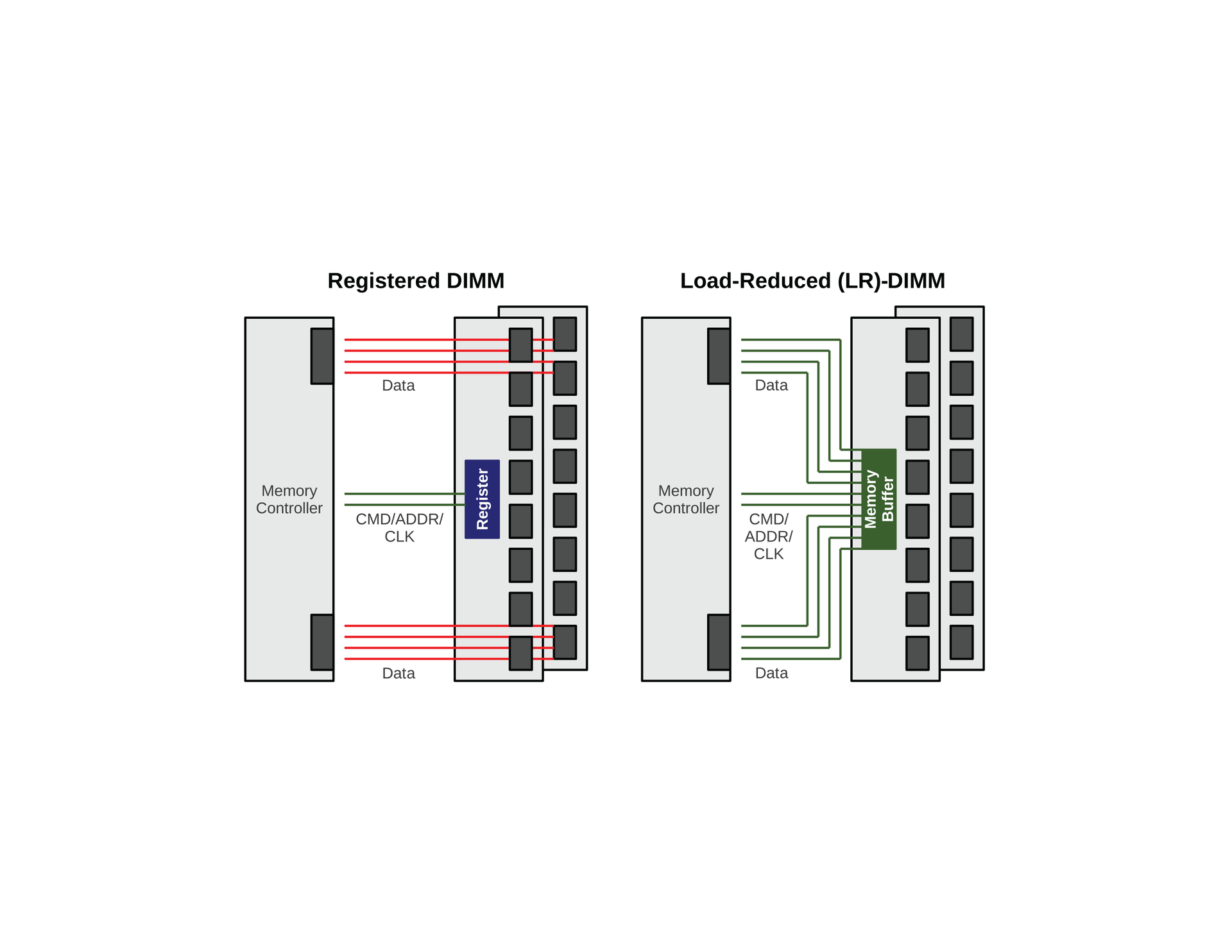

The Nehalem/Westmere microarchitecture that followed (Xeon 5500 and 5600) replaced FB-DIMMs with registered DIMMs on the basis of DDR3. The CMD/ADDR/CLK signal lines run through the register chip, but not the actual data connections. This means considerably reduced energy requirements compared with FB-DIMMs. LR-DIMMs (Figure 1), which are just around the corner, take this one step further.

LR-DIMMs have an Isolation Memory Buffer (iMB) through which all the signal lines run, but the iMB doesn't use a special signal protocol (like the AMB on FB-DIMMs); it works just like normal registered DIMMs. Thus, the iMB hardly increases power consumption. Because all of the signal lines run through the iMB on LR-DIMMs, the electrical load on the memory controller is lower compared with registered DIMMs. From the memory controller's point of view, LR-DIMMs act like single-rank modules. The dual-CPU systems in the Sandy Bridge microarchitecture expected in 2012 will be the first to support LR-DIMMs.

Rank

DIMMs always have a number of memory chips soldered onto them. The individual chips can use four (x4), eight (x8), or 16 (x16) signal lines. The signal lines on the memory controller are directly connected to the memory chips in the case of unbuffered DIMMs, so x4 chips are disqualified here – they can only be used in combination with buffer chips.

The memory area uniquely addressable by the memory controller has 64 (non-ECC) or 72 (ECC) signal lines and is referred to as a rank. For non-ECC memory modules, a rank can thus comprise either eight x8 chips, or four x16 chips. Memory modules populated with a single rank are referred to as single-rank modules and modules with two ranks as dual-rank modules. A single dual-rank DIMM puts the same load on the memory bus as two single-rank DIMMs.

In desktop applications, memory controllers support up to four ranks per memory channel, which is equivalent to two dual-rank DIMMs. Desktop mainboards with two memory controllers (dual-channel) thus typically have four RAM slots. Some boards have six slots; however, they only support one dual-rank DIMM in combination with two single-rank DIMMs per channel. Boards with three memory controllers (triple channel) typically still have four RAM slots: two slots for channel A and one slot each for channels B and C.

Green RAM

Besides the development of FB-DIMMs toward registered DIMMs and LR-DIMMs, technology has also made progress in reducing energy. For example, operating voltage drops from 2.5V for DDR1 to 1.8V for DDR2, and 1.5V for DDR3. DDR3L (1.35V) and DDR3U (1.25V) are two further reductions before DDR4 drops to 1.2V. Continuous miniaturization of the chip manufacturing process also offers benefits in terms of energy: DDR1 started at 150nm; the structure widths dropped in both DDR2 and DDR3, and the first DDR4 prototypes are based on a 30nm manufacturing process. All told, these measures reduce the energy requirements per gigabyte of RAM from just under 7 watts for ECC DDR2 FB-DIMMs to a current figure of 0.54 watts for ECC DDR3 Registered DIMMs (Table 2).

Tabelle 2: Energy Consumption of Memory Modules (Source: ATP)

|

Memory Module |

Capacity (GB) |

Memory Type |

Power Consumption (W) |

Power Consumption (W/GB) |

|---|---|---|---|---|

|

AL48M72F4GKF8S |

16 |

DDR3, Registered, ECC, 4 rank |

8.710 |

0.54 |

|

AL24M72E4BKH9S |

8 |

DDR3, Registered, ECC, 2 rank |

6.132 |

0.77 |

|

AL12M72B8BKH9S |

4 |

DDR3, Registered, ECC, 2 rank, memory chips with 256Mx8 organization (2-Gb chips) |

2.934 |

0.73 |

|

AL56M72B8BJH9S |

2 |

DDR3, Registered, ECC, 2 rank, memory chips with 128Mx8 organization (1-Gb chips) |

5.132 |

2.57 |

|

AL28M72A8BJH9S |

1 |

DDR3, Registered, ECC, 1 rank |

2.241 |

2.24 |

|

AQ12M72E8BKH9S |

4 |

DDR3, Unbuffered, ECC, 2 rank, memory chips with 256Mx8 organization (2-Gb chips) |

2.214 |

0.55 |

|

AQ28M72D8BJH9S |

1 |

DDR3, Unbuffered, ECC, 1 rank |

1.387 |

1.39 |

|

AJ28K72F8BJE6S |

1 |

DDR2, Unbuffered, ECC |

1.872 |

1.87 |

|

AP56K72G4BHE6S |

2 |

DDR2, FB-DIMM, ECC |

13.683 |

6.84 |